AI in the Cleanroom: How Deep Learning is Saving the Next Generation of Chips

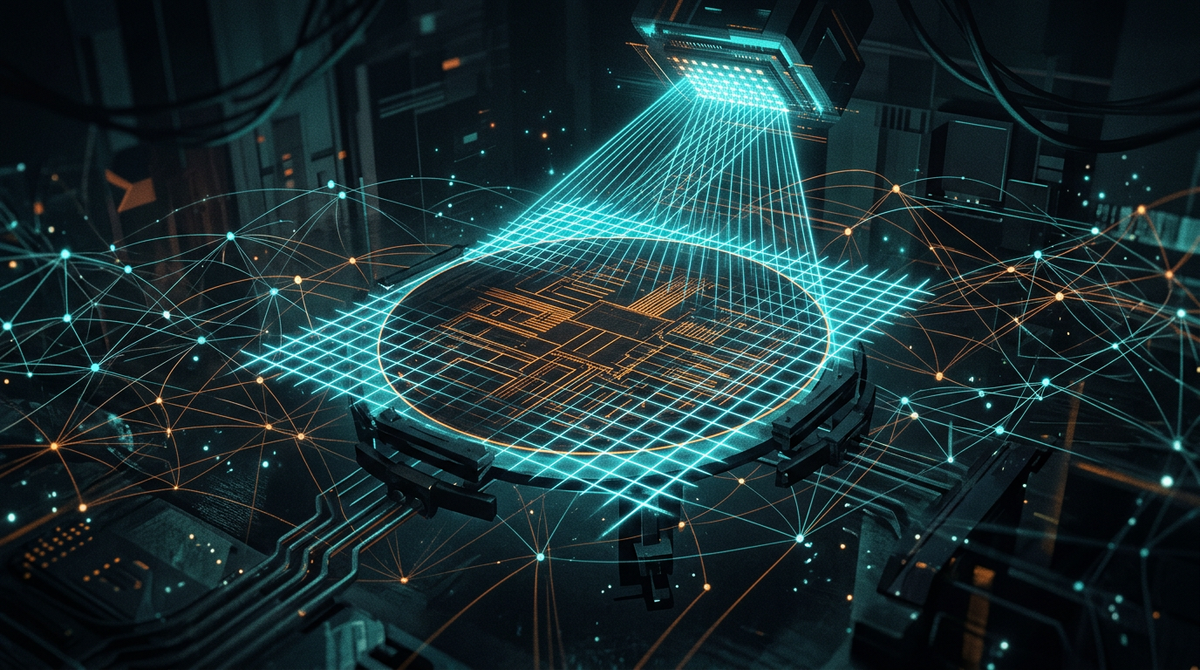

The semiconductor industry is turning to deep learning and AI-driven metrology to enhance chip yields at the nanometer scale. Advanced inspection systems are now capable of detecting sub-microscopic defects that previous generations of hardware would have missed.

As semiconductor manufacturing pushes into the sub-2nm era, the margin for error has virtually disappeared. To combat this, the industry is increasingly relying on AI-powered metrology and inspection. Traditional rule-based systems are no longer sufficient to identify the complex defects that occur during extreme ultraviolet (EUV) lithography. Instead, deep learning models are being integrated directly into the fabrication process to flag anomalies in real-time.

AI-driven inspection works by atmospheric analysis of billions of data points generated during the chip-making process. By training neural networks on "golden" wafer samples, these systems can identify "nuisance" defects—cosmetic issues that don't affect performance—and distinguish them from critical failures that would lead to a dead chip. This ability to filter noise drastically reduces the time engineers spend on manual review, accelerating the launch of new processor architectures.

Furthermore, the shift toward heterogeneous integration and chiplet designs has introduced new failure modes at the bonding interfaces. AI metrology tools are now being used to verify the alignment and electrical connectivity of these complex 3D structures. As the demand for AI hardware itself grows, the semiconductor industry is finding its greatest efficiency gains by applying AI to its own production lines. The "Smart Advantage" in manufacturing is no longer an option; it is a necessity for economic survival in the global chip race.

Source: Semiconductor Engineering